アドバンストパッケージング

TSV(Through-Silicon Via)向けSiエッチング、およびPECVDソリューション

TSVによるアドバンストパッケージング ── 高密度・高速化を実現する技術

3D構造を用いたパッケージング技術、とりわけシリコン貫通電極 (TSV:Through-Silicon Via) は、先端半導体デバイスの高性能化に欠かせません。高性能コンピューティング (HPC) やモバイル機器、そして新たなAI・エッジデバイスに至るまで、TSVは高速な接続、小型化、省電力化を実現します。

半導体業界が垂直方向の集積化を進める中で、TSV構造における高精度・高速・低ダメージなプロセス技術の重要性は、ますます高まっています。

TSV実装における製造課題

TSV構造の形成には、装置性能とプロセス制御の両面で高度な要件が求められます。主な課題は次のとおりです:

-

- エッチング速度と均一性TSVでは、高アスペクト比かつ深いビアをシリコン基板に高速かつ安定してエッチングする必要があります。量産を見据えた場合、とくにスループットが重要です。

-

- プロセスの選択 (ボッシュプロセスと非ボッシュプロセス) どちらの手法も使用されていますが、深掘り構造においては、側壁保護とエッチング制御に優れたボッシュプロセスが多くの用途で選ばれています。

-

- サーマルバジェット (熱履歴) の制約

- サーマルバジェット (熱履歴) の制約 後工程の接合や金属配線処理では、しばしばサーマルバジェットの抑制が求められます。そのため、膜質を維持しつつ低温で成膜可能な誘電体堆積プロセスが必要となります。

-

- プロファイル制御と残渣の最小化

- スキャロップやボウイング、ポリマ残渣の抑制は、電気的・構造的な信頼性を確保する上で不可欠です。

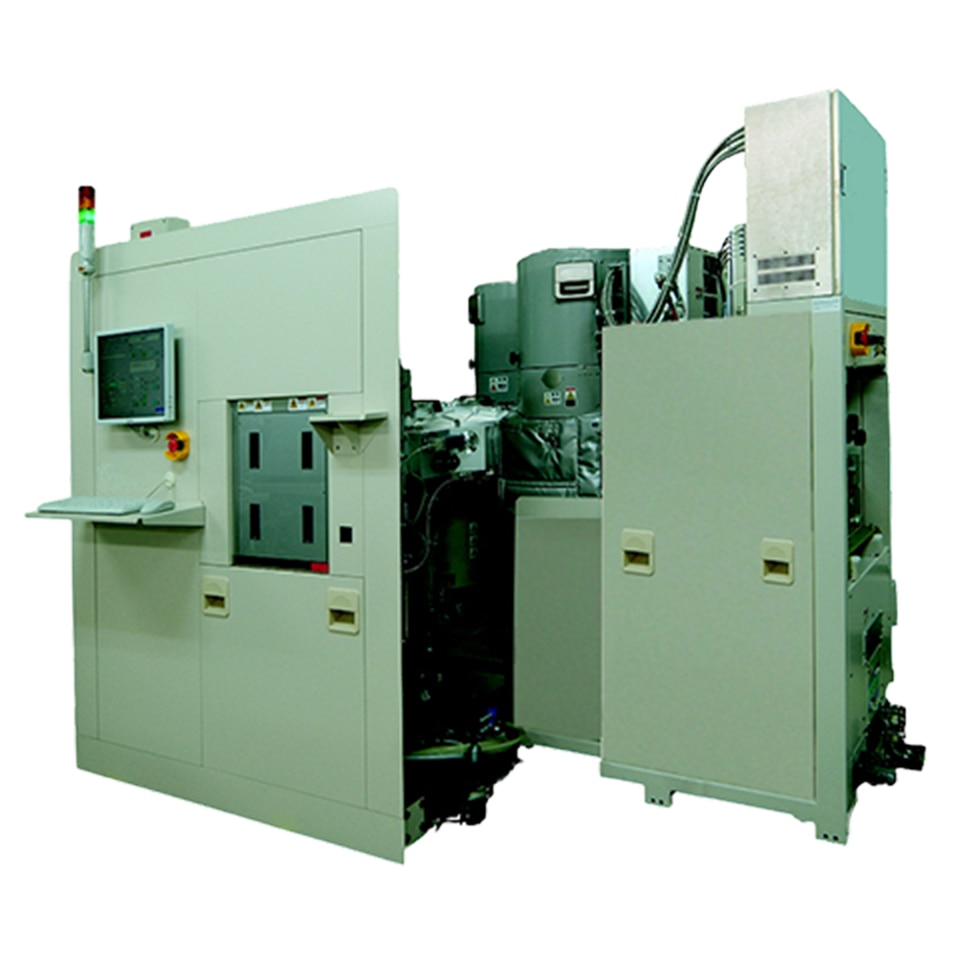

TSV向けSPTのエッチング、およびPECVDソリューション

SPTは、アドバンストパッケージングに求められる精度・スループット・信頼性に応える、専用設計のSi DRIEおよびPECVD装置を提供しています。

1. シリコン深掘りエッチング (Si DRIE)

- ボッシュプロセスを用いた高速シリコンエッチング

- 優れた側壁保護性能と最小限のスカラップ

- 深いビアや厚い基板への安定した対応力

2. 低温PECVD

- SiO₂およびSiNₓの高品質膜を低熱予算で形成

- 層間絶縁膜に適した膜厚・応力の精密制御

- TSVの絶縁・パッシベーションステップに最適

アドバンストパッケージングのプロセス別SPTソリューション

SPTは、TSVベースのアドバンストパッケージングにおける各工程を、装置と技術で支えています。

以下のプロセスフローを通じて、それぞれに対応するエッチング・成膜ソリューションをご覧いただけます。