蚀刻技术

探索SPT的高性能干法蚀刻技术——涵盖深硅蚀刻 (Si DRIE) 、反应性离子蚀刻 (RIE) 与牺牲层蚀刻,广泛应用于MEMS、TSV与化合物半导体领域。

蚀刻概述

蚀刻是半导体制造中的关键工艺,用于精准去除材料,以在晶圆上形成所需图形与结构。

SPT专注于基于等离子体的干法蚀刻技术,涵盖Si DRIE、RIE与牺牲层蚀刻,专为高深宽比结构、低损伤与工艺均匀性而设计,广泛服务于MEMS与先进器件制造。

什么是半导体蚀刻?

蚀刻是通过掩膜图案从半导体晶圆上选择性去除特定材料层的工艺。

主要分为两类:

– 湿法蚀刻:使用液态化学试剂

– 干法蚀刻:在真空中使用等离子体或反应性气体

SPT专注于干法蚀刻技术,提供适用于MEMS、TSV与化合物半导体等复杂结构的高精度、清洁的图形转移方案。

蚀刻工艺类型:干法 vs 湿法

半导体蚀刻大致可分为湿法与干法两类,两者各有优劣。

以下表格总结了主要差异,随后我们将进一步介绍各自特性。

| 特性 | 湿法蚀刻 | 干法蚀刻 (基于等离子体) |

|---|---|---|

| 蚀刻介质 | 液态化学试剂 | 反应性气体或等离子体 |

| 蚀刻方向性 | 各向同性 (多方向) | 各向异性 (垂直、可控) |

| 材料选择性 | 通常较高 | 可通过工艺条件调节 |

| 图形分辨率 | 受限 (易产生侧蚀) | 高分辨率,精细结构控制能力强 |

| 设备复杂性 | 相对简单 | 需要真空腔体与射频电源 |

| 适用场景 | 大面积或非关键图形处理 | 先进MEMS、TSV、高深宽比结构 |

各工艺优势概览

湿法蚀刻具备成本低、工艺简单的优点;

而干法蚀刻则提供先进半导体工艺所需的高精度与可控性。

晶圆被浸入化学溶液中以溶解目标材料。

尽管简便且经济,但其各向同性蚀刻特性使其不适合处理微缩或垂直结构。

干法蚀刻在真空腔体中使用等离子体或反应性气体,具有高度方向性。

可实现复杂图形的精确各向异性蚀刻,是MEMS、TSV与先进节点器件制造的关键技术。

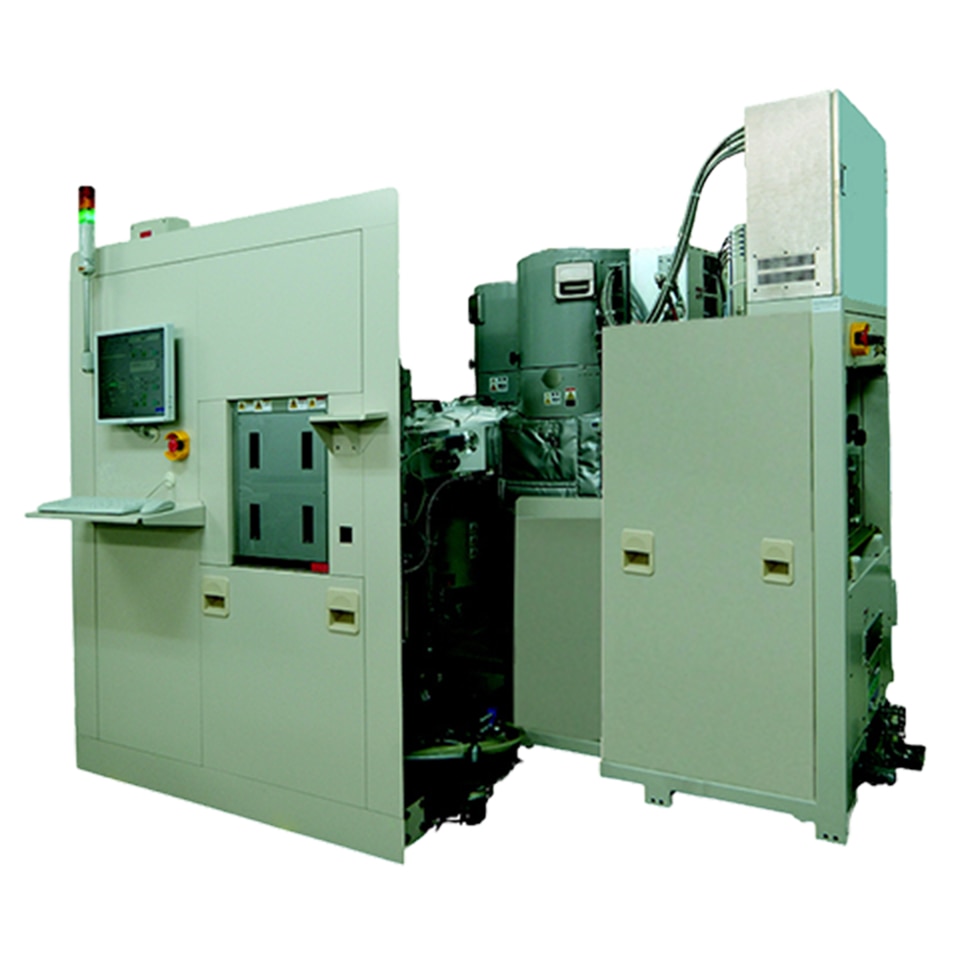

SPT的干法蚀刻系统具备优异的均匀性、支持高深宽比结构,并有效控制工艺损伤。

SPT的等离子体蚀刻技术

SPT提供三种基于等离子体的干法蚀刻技术,分别针对深层结构、耐蚀材料与敏感结构释放等多种应用需求。

深硅蚀刻 (Si DRIE)

Si DRIE是一种用于硅材料的深蚀刻工艺,具备高深宽比与垂直侧壁特性。

SPT的Si DRIE系统采用Bosch工艺,具备高速、高精度与卓越均匀性,广泛用于MEMS与TSV制造。

反应性离子蚀刻 (RIE)

RIE是一种具备方向性与精细控制的等离子蚀刻技术。

SPT的RIE系统适用于化合物半导体、二氧化硅与各类介质材料的高精度蚀刻,具备出色的均匀性与低损伤控制。

典型应用包括功率器件、光子结构与LED制造。

牺牲层蚀刻

牺牲层蚀刻用于释放MEMS结构,通过干式蒸汽蚀刻方式去除埋藏的二氧化硅层,避免吸附与损伤。

SPT的无水HF蒸汽蚀刻系统可实现选择性去除牺牲层,保护铝等敏感材料,实现洁净、稳定的结构释放。