先进封装与

面向TSV集成的先进Si DRIE与PECVD解决方案

基于TSV的先进封装:实现高密度与高速性能的关键

三维(3D)封装技术,尤其是硅通孔(TSV),是提升先进半导体器件性能的核心手段。

从高性能计算(HPC)、移动设备,到新兴的人工智能与边缘计算应用,TSV支持更快的互连、更小的封装面积与更高的能效。

随着半导体产业向垂直集成持续演进,TSV结构的高精度、高速度与低损伤加工需求也日益迫切。

高密度封装中TSV制造的关键挑战

TSV结构对设备性能与工艺控制提出了独特要求,主要挑战包括:

-

- 蚀刻速度与均匀性:

- TSV通常需要深度大、深宽比高的通孔结构,必须在保持高速的同时确保硅蚀刻的一致性。尤其在量产环境下,高产能与工艺稳定性至关重要。

-

- 工艺路线选择(Bosch vs 非Bosch):

- 两种方式皆可用于TSV制造,但Bosch工艺在侧壁保护与深结构控制方面更具优势,是许多应用中的优选方案。

-

- 热预算限制:

- 后续的键合或金属化步骤对热预算要求严格,因此介电膜沉积需在低温下依然保持高膜质与稳定性。

-

- 轮廓控制与残留最小化:

- 控制边缘锯齿、侧壁弯曲与聚合物残留至关重要,以保障电气性能与结构完整性。

SPT为TSV应用打造的蚀刻与沉积解决方案

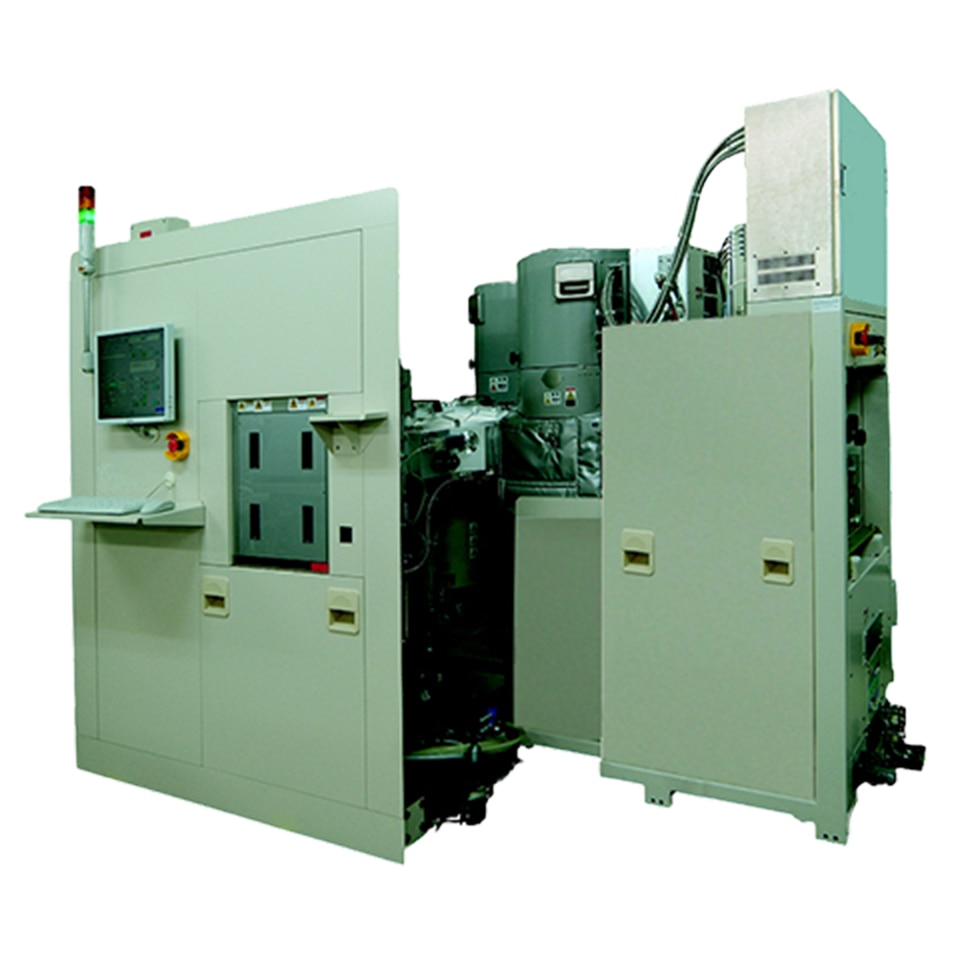

SPT提供专为先进封装设计的Si DRIE与PECVD系统,满足高精度、高产能与高可靠性的制造需求。

1. 硅深反应离子蚀刻(Si DRIE)

- 采用Bosch工艺实现高速硅蚀刻

- 出色的侧壁保护,边缘锯齿最小化

- 稳定适用于深通孔与厚基板处理

2. 低温PECVD

- 在低热预算下沉积高质量SiO₂与SiNₓ薄膜

- 精准控制层间介电膜的厚度与应力

- 理想选择用于TSV绝缘与钝化步骤

与SPT共探TSV封装工艺流程

了解SPT如何支持基于TSV的先进封装制造中的各个关键阶段。

以下卡片链接至匹配的设备与解决方案: